掌握ESD保护技巧,提高电子产品可靠性

2024-06-11

掌握ESD保护技巧,提高电子产品可靠性

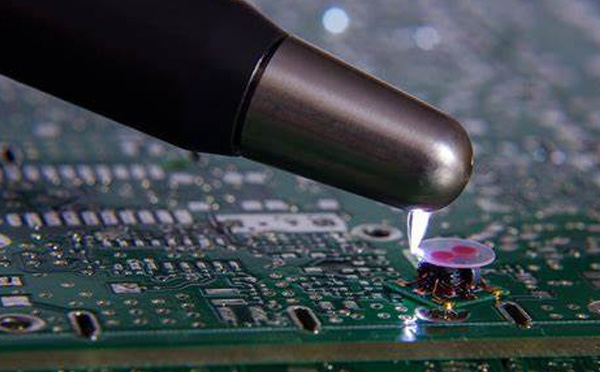

在ESD的破坏中,静电会对I/O端口造成毁灭性损害,有可能造成数据位重影、产品损坏直至造成电子设备“硬故障”或元器件损坏。所以工程师需要考虑设计中的ESD问题并掌握解决之道。

目前便携产品中越来越多的采用低功率逻辑芯片,由于金属氧化半导体(MOS)电介质击穿和双极反向结电流的限制,这些逻辑芯片对 ESD非常敏感。控制I/O端口(USB端口、以太网端口等)的IC芯片更不例外,因为它们大多数都是以CMOS工艺为基础来设计和制造的,这导致IC芯 片对ESD造成的损害非常敏感。另外,大多数的I/O端口(尤其是USB端口)都是热插拔系统,极易受到由用户或空气放电造成的ESD影响。由此可见,ESD保护在当今的便携和USB应用中是非常必要的。瑞隆源电子特别针对USB应用设备提出了解决方案.

有工程师对T1/E1接口设计中加装TVS器件后的保护作用提出疑问,3499cc拉斯维加斯认为在电源线上增加TVS器件有助于解决来自电源端口的ESD问题,并强调TVS要连接到电源的Vcc和地以防止电源出现ESD干扰。

在回答工程师提出的有关综合考虑ESD保护的问题时,3499cc拉斯维加斯认为综合考虑ESD保护要从三个方面入手:1、芯片的ESD容量;2、PCB版图设 计;3、机械设计。他表示好的PCB版图设计应该尽量增大接地面积、缩短PCB走线,他特别强调TVS阵列可以有效解决ESD问题。

针对ESD引起的共模干扰,3499cc拉斯维加斯指出通常可以使用共模扼流圈或TVS阵列来解决ESD问题和完成EMI滤波,在电路中共模扼流圈串行连接,TVS并行接在电路中。除考虑用器件解决ESD问题外,我们也可以遵循一些基本规则来解决PCB的ESD问题:

1、尽可能使用多层PCB 相对于双面PCB而言,地平面和电源平面以及排列紧密的信号线-地线间距能够减小共模阻抗(common impedance)和感性耦合,使之达到双面PCB的1/10到1/100。

2、尽量地将每一个信号层都紧靠一个电源层或地线层。对于顶层和底层表面都有元器件、具有很短连接线以及许多填充地的高密度PCB,可以考虑使用内层线。大多数的信号线以及电源和地平面都在内层上,因而类似于具备屏蔽功能的法拉第盒。

3、对于双面PCB来说,要采用紧密交织的电源和地栅格。通常的解决原则是要通过测试-解决问题-重新测试这样的周期,每一个周期都可能至少影响到一块PCB的设计。在PCB设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。

上一篇:

下一篇:

热门文章

2026-02-02

岁末同欢·感恩同行——3499cc拉斯维加斯2025年第四季度员工生日会圆满举办

2025-12-29

2025-09-30

金秋送爽,同心筑梦—2025年3499cc拉斯维加斯第三季度员工生日会

2025-09-25

骄阳似火,时光共鉴——3499cc拉斯维加斯二季度员工集体生日会

2025-06-30

粽香情浓 暖心相伴—3499cc拉斯维加斯为全体员工送上端午福利

2025-05-30

3499cc拉斯维加斯(深圳)有限公司

深圳市宝安区石岩街道德政路高科工业区森海诺科创大厦7楼

工厂地址:河南省焦作市武陟县木栾街道郑北大道与覃怀大道交叉口智能硬件产业港6号楼